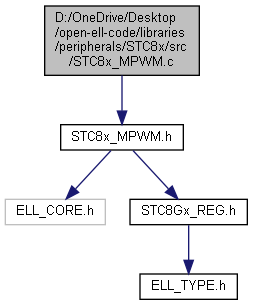

#include "STC8x_MPWM.h"

宏定义 | |

| #define | clrBitENGLBSET() PWMSET&=(~ENGLBSET) |

| #define | setBitENGLBSET() PWMSET|=( ENGLBSET) |

| #define | clrBitPWMRST() PWMSET&=(~PWMRST) |

| #define | setBitPWMRST() PWMSET|=( PWMRST) |

| #define | PWM_ENABLE(PORT) PWMSET|=(1<<PORT) |

| #define | PWM_DISABLE(PORT) PWMSET&=(~(1<<PORT)) |

| #define | clrBitPWMnCBIF(PORT) |

| #define | clrBitEPWMnCBI(PORT) |

| #define | setBitEPWMnCBI(PORT) |

| #define | clrBitPWMnCEN(PORT) |

| #define | setBitPWMnCEN(PORT) |

| #define | clrBitENPWMnTA(PORT) |

| #define | setBitENPWMnTA(PORT) |

| #define | setRegPWMnFDCR(PORT, VALUE) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | (PORT%3*0x50+0x06))) = VALUE |

| #define | setRegPWMnC(PORT, VALUE) ( *(__IO uint16_t xdata *) ((0xFF-(PORT/3*3))<<8 | (PORT%3*0x50+0x00))) = VALUE |

| #define | setRegPWMnCKS(PORT, VALUE) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | (PORT%3*0x50+0x02))) = VALUE |

| #define | setRegPWMnTADC(PORT, VALUE) ( *(__IO uint16_t xdata *) ((0xFF-(PORT/3*3))<<8 | (PORT%3*0x50+0x03))) = VALUE |

| #define | setRegPWMniT1(PORT, CHANNEL, VALUE) ( *(__IO uint16_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 0))) = VALUE |

| #define | setRegPWMniT1H(PORT, CHANNEL, VALUE) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 0))) = VALUE |

| #define | setRegPWMniT1L(PORT, CHANNEL, VALUE) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 1))) = VALUE |

| #define | setRegPWMniT2(PORT, CHANNEL, VALUE) ( *(__IO uint16_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 2))) = VALUE |

| #define | setRegPWMniT2H(PORT, CHANNEL, VALUE) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 2))) = VALUE |

| #define | setRegPWMniT2L(PORT, CHANNEL, VALUE) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 3))) = VALUE |

| #define | setRegPWMniCR(PORT, CHANNEL, VALUE) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) = VALUE |

| #define | setBitPWMniEnableOut(PORT, CHANNEL) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) |=( ENO) |

| #define | clrBitPWMniEnableOut(PORT, CHANNEL) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) &=(~ENO) |

| #define | setBitPWMniStartLevel(PORT, CHANNEL) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) |=( INI) |

| #define | clrBitPWMniStartLevel(PORT, CHANNEL) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) &=(~INI) |

| #define | setBitPWMniEnableIntrupt(PORT, CHANNEL) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) |=( ENI) |

| #define | clrBitPWMniEnableIntrupt(PORT, CHANNEL) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) &=(~ENI) |

| #define | setBitPWMniEnableIntruptAtTrig2(PORT, CHANNEL) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) |=( ENT2I) |

| #define | clrBitPWMniEnableIntruptAtTrig2(PORT, CHANNEL) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) &=(~ENT2I) |

| #define | setBitPWMniEnableIntruptAtTrig1(PORT, CHANNEL) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) |=( ENT1I) |

| #define | clrBitPWMniEnableIntruptAtTrig1(PORT, CHANNEL) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) &=(~ENT1I) |

| #define | setRegPWMniHLD(PORT, CHANNEL, VALUE) ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 5))) = VALUE |

| #define | clrBitPWMniIF(PORT, CHANNEL) ( *(__IO uint16_t xdata *) ((0xFF-(PORT/3*3))<<8 | (PORT%3*0x50+0x05))) &= (~(1<<CHANNEL)) |

函数 | |

| FSCSTATE | MPWMn_Port_Init (MPWMPort_Type port, MPWMCLKSrc_Type clkSrc, uint16_t period) |

| PWM端口初始化函数。Init PWM port function. 更多... | |

| FSCSTATE | MPWMn_Channel_Init (MPWMPort_Type port, MPWMChannel_Type ch, MPWMStartLevel_Type level, uint16_t fValue, uint16_t sValue, BOOL run) |

| PWM通道初始化函数。Init PWM channel function. 更多... | |

| FSCSTATE | MPWMn_Run (MPWMPort_Type port) |

| 指定PWM端口开始工作。Run specified PWM port. 更多... | |

| FSCSTATE | MPWMn_Stop (MPWMPort_Type port) |

| 指定PWM端口停止工作。Stop specified PWM port working. 更多... | |

变量 | |

| sfr | PWMSET = PWMSET_ADDRESS |

| #define clrBitENPWMnTA | ( | PORT | ) |

| #define clrBitEPWMnCBI | ( | PORT | ) |

| #define clrBitPWMnCBIF | ( | PORT | ) |

| #define clrBitPWMnCEN | ( | PORT | ) |

| #define clrBitPWMniEnableIntrupt | ( | PORT, | |

| CHANNEL | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) &=(~ENI) |

| #define clrBitPWMniEnableIntruptAtTrig1 | ( | PORT, | |

| CHANNEL | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) &=(~ENT1I) |

| #define clrBitPWMniEnableIntruptAtTrig2 | ( | PORT, | |

| CHANNEL | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) &=(~ENT2I) |

| #define clrBitPWMniEnableOut | ( | PORT, | |

| CHANNEL | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) &=(~ENO) |

| #define clrBitPWMniIF | ( | PORT, | |

| CHANNEL | |||

| ) | ( *(__IO uint16_t xdata *) ((0xFF-(PORT/3*3))<<8 | (PORT%3*0x50+0x05))) &= (~(1<<CHANNEL)) |

| #define clrBitPWMniStartLevel | ( | PORT, | |

| CHANNEL | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) &=(~INI) |

| #define PWM_DISABLE | ( | PORT | ) | PWMSET&=(~(1<<PORT)) |

| #define PWM_ENABLE | ( | PORT | ) | PWMSET|=(1<<PORT) |

| #define setBitENPWMnTA | ( | PORT | ) |

| #define setBitEPWMnCBI | ( | PORT | ) |

| #define setBitPWMnCEN | ( | PORT | ) |

| #define setBitPWMniEnableIntrupt | ( | PORT, | |

| CHANNEL | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) |=( ENI) |

| #define setBitPWMniEnableIntruptAtTrig1 | ( | PORT, | |

| CHANNEL | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) |=( ENT1I) |

| #define setBitPWMniEnableIntruptAtTrig2 | ( | PORT, | |

| CHANNEL | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) |=( ENT2I) |

| #define setBitPWMniEnableOut | ( | PORT, | |

| CHANNEL | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) |=( ENO) |

| #define setBitPWMniStartLevel | ( | PORT, | |

| CHANNEL | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) |=( INI) |

| #define setRegPWMnC | ( | PORT, | |

| VALUE | |||

| ) | ( *(__IO uint16_t xdata *) ((0xFF-(PORT/3*3))<<8 | (PORT%3*0x50+0x00))) = VALUE |

| #define setRegPWMnCKS | ( | PORT, | |

| VALUE | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | (PORT%3*0x50+0x02))) = VALUE |

| #define setRegPWMnFDCR | ( | PORT, | |

| VALUE | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | (PORT%3*0x50+0x06))) = VALUE |

| #define setRegPWMniCR | ( | PORT, | |

| CHANNEL, | |||

| VALUE | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x14) + 0))) = VALUE |

| #define setRegPWMniHLD | ( | PORT, | |

| CHANNEL, | |||

| VALUE | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 5))) = VALUE |

| #define setRegPWMniT1 | ( | PORT, | |

| CHANNEL, | |||

| VALUE | |||

| ) | ( *(__IO uint16_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 0))) = VALUE |

| #define setRegPWMniT1H | ( | PORT, | |

| CHANNEL, | |||

| VALUE | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 0))) = VALUE |

| #define setRegPWMniT1L | ( | PORT, | |

| CHANNEL, | |||

| VALUE | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 1))) = VALUE |

| #define setRegPWMniT2 | ( | PORT, | |

| CHANNEL, | |||

| VALUE | |||

| ) | ( *(__IO uint16_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 2))) = VALUE |

| #define setRegPWMniT2H | ( | PORT, | |

| CHANNEL, | |||

| VALUE | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 2))) = VALUE |

| #define setRegPWMniT2L | ( | PORT, | |

| CHANNEL, | |||

| VALUE | |||

| ) | ( *(__IO uint8_t xdata *) ((0xFF-(PORT/3*3))<<8 | ((CHANNEL*0x08+PORT%3*0x50+0x10) + 3))) = VALUE |

| #define setRegPWMnTADC | ( | PORT, | |

| VALUE | |||

| ) | ( *(__IO uint16_t xdata *) ((0xFF-(PORT/3*3))<<8 | (PORT%3*0x50+0x03))) = VALUE |

| FSCSTATE MPWMn_Channel_Init | ( | MPWMPort_Type | port, |

| MPWMChannel_Type | ch, | ||

| MPWMStartLevel_Type | level, | ||

| uint16_t | fValue, | ||

| uint16_t | sValue, | ||

| BOOL | run | ||

| ) |

PWM通道初始化函数。Init PWM channel function.

初始化指定端口(0-5)的指定通道(0-7)。Init the specified port's channel (port from 0 to 5, channel from 0 to 7)

| [in] | port | PWM端口枚举体。PWM port enumerator. |

| [in] | ch | PWM通道枚举体。PWM channel enumerator. |

| [in] | level | PWM开始电平。PWM start level. |

| [in] | fValue | 第一个电平翻转点。The value of the first reversal point. |

| [in] | sValue | 第二个电平翻转点。The value of the second reversal point. |

| [in] | run | 运行控制位。Run control bit. |

| FSCSTATE MPWMn_Port_Init | ( | MPWMPort_Type | port, |

| MPWMCLKSrc_Type | clkSrc, | ||

| uint16_t | period | ||

| ) |

PWM端口初始化函数。Init PWM port function.

初始化指定端口(0-5)。Init the specified PWM port. (from 0 to 5)

| [in] | port | PWM端口枚举体。PWM port enumerator. |

| [in] | clkSrc | PWM时钟源。PWM clock source. |

| [in] | period | PWM周期值(计数器重装载值)。PWM period value (counter reload value) |

| FSCSTATE MPWMn_Run | ( | MPWMPort_Type | port | ) |

指定PWM端口开始工作。Run specified PWM port.

指定PWM端口开始工作,输出PWM波形。Run specified PWM port. (Start PWM signal outputs)

| [in] | port | PWM端口枚举体。PWM port enumerator. |

| FSCSTATE MPWMn_Stop | ( | MPWMPort_Type | port | ) |

指定PWM端口停止工作。Stop specified PWM port working.

指定PWM端口停止工作,停止输出PWM波形。Stop specified PWM port. (Stop PWM signal outputs)

| [in] | port | PWM端口枚举体。PWM port enumerator. |

| sfr PWMSET = PWMSET_ADDRESS |